DOI: 10.15514/ISPRAS-2025-37(1)-8

# САПР для удаленного высокоуровневого моделирования СтнК

А.А. Американов, ORCID: 0000-0002-5970-2125 < aamerikanov@hse.ru>

Л.Г. Евтушенко, ORCID: 0000-0003-1261-9735 < levtushenko@hse.ru>

В.В. Зунин, ORCID: 0000-0002-9117-4879 < vzunin@hse.ru>

В.М. Винарский, ORCID: 0009-0005-5319-6304 < vmvinarskiy@edu.hse.ru>

Национальный исследовательский университет «Высшая школа экономики»,

Россия, 101000, г. Москва, ул. Мясницкая, д. 20.

Аннотация. Статья посвящена описанию процесса создания новой архитектуры САПР для высокоуровневого моделирования СтнК, а также удаленному маршруту проектирования СтнК. В работе проведен анализ основных этапов проектирования СтнК, в результате чего продемонстрирована высокая значимость высокоуровневого моделирования и его влияние на весь процесс проектирования. Также рассмотрена возможность проведения высокоуровневого моделирования в удаленном формате с использованием клиент-серверной архитектуры, предложенной САПР. Рассмотрен процесс удаленного проектирования СтнК с использованием предложенного САПР и удаленных стендов с отладочными платами ПЛИС.

**Ключевые слова:** система автоматизированного проектирования (САПР); высокоуровневое имитационное моделирование; сеть на кристалле (СтнК); проектирование СтнК; удаленные стенды.

**Для цитирования:** Американов А.А., Евтушенко Л.Г., Зунин В.В., Винарский В.М. САПР для удаленного высокоуровневого моделирования СтнК. Труды ИСП РАН, том 37, вып. 1, 2025 г., стр. 133–144. DOI: 10.15514/ISPRAS–2025–37(1)–8.

**Благодарности:** Публикация подготовлена в ходе проведения исследования (№ 24-00-012 «Удаленная лаборатория для работы со встраиваемыми системами») в рамках Программы «Научный фонд Национального исследовательского университета «Высшая школа экономики» (НИУ ВШЭ)».

### **CAD for Remote High-Level Modeling of NoC**

A.A. Amerikanov, ORCID: 0000-0002-5970-2125 <aamerikanov@hse.ru> L.G. Evtushenko, ORCID: 0000-0003-1261-9735 <levtushenko@hse.ru> V.V. Zunin, ORCID: 0000-0002-9117-4879 <vzunin@hse.ru> V.M. Vinarskii, ORCID: 0009-0005-5319-6304 <vmvinarskiy@edu.hse.ru>

> HSE University, 20, Myasnitskaya st., Moscow, 101000, Russia.

**Abstract.** The paper is devoted to the description of the process of developing a new CAD architecture for high-level modeling of NoC, as well as the remote flow of NoC design. The paper analyzes the main stages of NoC design and demonstrates the high importance of high-level modeling and its impact on the entire design process. Also, the possibility of conducting high-level modeling in a remote format using the client server architecture of the CAD is considered. The process of remote design of NoC using the proposed CAD system and remote testbed with FPGA debug boards is demonstrated.

**Keywords:** computer-aided design (CAD); high-level modeling; network-on-chip (NoC); NoC design; remote testbed.

**For citation:** Amerikanov A.A., Evtushenko L.G., Zunin V.V., Vinarskii V.M. CAD for remote high-level modeling of NoC. *Trudy ISP RAN/Proc. ISP RAS*, vol. 37, issue 1, 2025, pp. 133-144. DOI: 10.15514/ISPRAS-2025-37(1)-8.

**Acknowledgements.** The publication was prepared within the framework of the Academic Fund Program at HSE University (grant N 24-00-012 Remote laboratory for working with embedded systems).

#### 1. Введение

С каждым годом растет сложность решаемых задач и объем информации, которую требуется обрабатывать, а значит растут и требования, предъявляемые к производительности систем на кристалле [1]. Задачи, требующие высокой вычислительной производительности, и задачи по работе с большим потоком данных не всегда могут быть эффективно решены с помощью однопроцессорных систем [2]. Увеличение плотности размещения транзисторов на чипе становится все более сложным, в связи с чем происходит эволюция вычислительных систем в сторону многоядерности, многопоточности и использования специализированных вычислительных ядер и ускорителей [3, 4]. Чип WSE2 от компании Cerebras [5] является ярким примером экстенсивного увеличения количества ядер на одном чипе; он выполнен по 7 нанометровому техпроцессу и состоит из 850000 вычислительных узлов. Также существует тенденция к замене громоздкой CISC архитектуры [6] на сети из процессорных ядер, разработанных на основе RISC архитектуры [7]. Из этого следует повышение требований к подсистеме связи для объединения множества гетерогенных ядер в одну систему – сеть на кристалле (СтнК) [8].

Процесс проектирования СтнК можно разделить на несколько основных последовательных этапов [9]: подготовка технического задания, предварительное проектирование, высокоуровневое и низкоуровневое моделирование, прототипирование или косимуляция, производство. Для каждого этапа обычно используются различные специализированные системы автоматизации проектирования (САПР), но другим возможным решением является применение единого САПР для всего процесса в целом.

Этап высокоуровневого моделирования требуется, чтобы выделить ограниченное количество подходящих для дальнейшего проектирования наборов параметров и характеристик сети, заданных на стадиях составления технического задания и проектирования СтнК. Цена ошибки на этапе высокоуровневого моделирования очень высока, так как низкоуровневое моделирование представляет собой гораздо более длительный и трудоемкий процесс. Например, высокоуровневое моделирование сети на 100 узлов с использованием

высокоуровневой модели OCNS (On-Chip Network Simulator) [10] может занимать несколько минут, в то время как низкоуровневое моделирование этой сети в программе моделирования, например ModelSim [11], может занять несколько дней.

Обычно на этапе высокоуровневого моделирования применяются имитационные модели [12]. Имитационная модель СтнК – это модель, в которой описаны основные моделируемые элементы сети и заданы правила взаимодействия между ними. Как правило, высокоуровневые модели используются для описания процесса передачи данных в СтнК и получения предварительных оценок ее характеристик при заданных параметрах. Процесс передачи данных является критически важным элементом функционирования сети. На этапе представления высокоуровневого моделирования точностью некоторых функционирования сети можно пренебречь, увеличив скорость расчета характеристик. В низкоуровневом моделировании напротив, учитывается как можно больше аспектов функционирования сети, например, учитывается реализация сложно-функциональных блоков, чтобы получить более точный результат моделирования.

Следует также отметить, что различные высокоуровневые модели решают разные, зачастую узкоспециализированные, задачи. Существует множество различных средств автоматизации моделирования СтнК и других вспомогательных средств, созданных разными разработчиками.

В проектировании нет единого подхода для объединения различных методов автоматизации проектирования СтнК на уровне архитектуры. Это позволило бы реализовать сквозное проектирование СтнК, используя разные модели и средства на разных этапах разработки, обеспечивая их совместимость через универсальные интерфейсы и форматы данных. Также обычно передача данных между этапами высокоуровневого и низкоуровневого моделирования в основном выполняется вручную, что приводит к увеличению трудозатрат и опибок [13]. Кроме того необходимо, чтобы была возможность проведения удаленного запуска сценариев моделирования на мощной вычислительной машине, чтобы не разворачивать средства моделирования на разных машинах. Таким образом, разработка единых средств анализа результатов высокоуровневого моделирования и автоматизации процесса моделирования являются важной и актуальной научно-практической задачей, которой посвящена данная статья.

Далее в разделе 2 сформулирована проблема, решаемая в данном исследовании. В разделе 3 проведен анализ цикла проектирования СтнК, приведена типовая схема проектирования СтнК, обоснована важность этапа высокоуровневого моделирования. В разделе 4 проведен краткий анализ высокоуровневых моделей СтнК. В разделе 5 описан процесс создания САПР для высокоуровневого моделирования СтнК, приведены схемы структуры и работы САПР и рассмотрен перенос предложенного САПР высокоуровневого моделирования СтнК на клиент-серверную архитектуру. Такой подход позволит выполнять этап высокоуровневого моделирования с использованием удаленных стендов, с возможностью последующего прототипирования и косимуляции.

## 2. Высокоуровневое моделирование СтнК

В настоящее время существует множество высокоуровневых моделей, предлагаемых к практическому использованию для моделирования СтнК. Авторами работы исследованы различные реализации высокоуровневых моделей, которые могут применяться для СтнК [14–17]. Они отличаются по множеству различных параметров, например, по функциональному назначению, типам трафика, областям применения. В настоящее время кажущееся многообразие не привело к появлению какой-либо универсальной модели, которая могла бы учитывать все возможные варианты конфигураций СтнК, и выполняла бы расчет всех возможных параметров сети. Обычно модель подбирается в зависимости от технических требований и решений, принятых на этапе проектирования. При этом большинство средств

моделирования СтнК не имеют каких-либо встроенных инструментов автоматизации расчетов (например, возможности запуска нескольких моделей одновременно или автоматического подбора параметров в зависимости от целей моделирования).

Из сказанного следует необходимость создания новых инструментов и методов автоматизации высокоуровневого моделирования СтнК, а также разработки единых средств автоматизации проектирования для проведения исследования характеристик СтнК, то есть существует потребность в создании САПР, которая имела бы возможность объединять в себе и сравнивать несколько высокоуровневых моделей и результаты их работы, тем самым увеличивая точность моделирования. Также объединение множества высокоуровневых моделей в единой САПР позволит сократить время моделирования путем применения методов оптимизации при поиске различных параметров СтнК.

Таким образом, проблема, решаемая в данном исследовании, заключается в существовании множества разнородных высокоуровневых моделей СтнК и отсутствии САПР, которая позволила бы объединить их в рамках единой среды проектирования, провести оценку достоверности результатов, а также сохранить результаты предыдущих циклов моделирования.

### 3. Анализ классического цикла проектирования сетей на кристалле

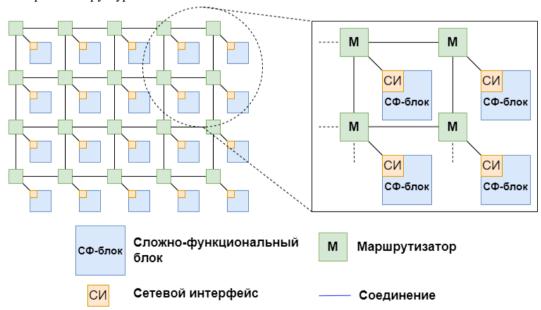

Для проектирования сложных многоядерных вычислительных систем все чаще используют архитектурные решения из области СтнК. СтнК – многопроцессорные системы на кристалле, где роль вычислительных узлов выполняют сложно функциональные блоки (СФ-блоки), которые связаны короткими соединениями на чипе для обмена информацией. На рис. 1 изображена структура СтнК.

Puc. 1. Структура СтнК. Fig. 1. NoC structure.

Особенностями СтнК являются ограниченность набора средств автоматизации основных этапов проектирования, из-за малого количества специализированных САПР для проектирования СтнК, и невозможность полного отображения алгоритмов, методов и протоколов маршрутизации, применяемых в классических сетях из-за ограниченных ресурсов.

### 3.1 Типовая схема проектирования сетей на кристалле

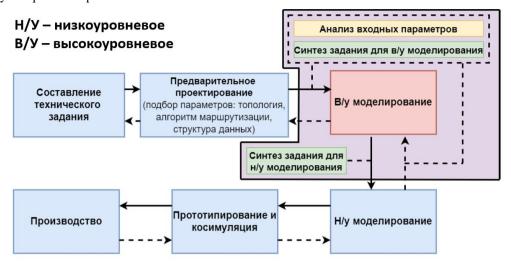

На рис. 2 приведена типовая схема проектирования СтнК. Сплошными стрелками на схеме показаны переходы к следующим этапам проектирования. Ошибки на разных этапах проектирования вынуждают разработчика возвращаться на предыдущий этап, что показано пунктирными стрелками на схеме.

Puc. 2. Типовая схема проектирования СтнК. Fig. 2. Typical scheme for NoC design.

На этапе подготовки технического задания, состоящего из определения желаемых характеристик СтнК, необходимо учитывать следующие параметры:

- 1) ограничения аппаратных ресурсов;

- 2) формат данных, передаваемых в СтнК между вычислительными ядрами;

- 3) область применения СтнК.

На этапе предварительного проектирования происходит:

- 1) выбор топологии;

- 2) выбор типа маршрутизации (детерминированная/адаптивная);

- 3) выбор типа данных, передаваемых между узлами;

- 4) выбор типа маршрутизаторов и вычислительных ядер.

Важным этапом проектирования является высокоуровневое моделирование. Данный этап позволяет отобрать ограниченное количество подходящих для дальнейшего проектирования наборов параметров и характеристик сети, выбранных на стадии проектирования СтнК.

Основными оцениваемыми параметрами являются:

- 1) максимальный/минимальный путь пакета;

- 2) отказоустойчивость (для адаптивных алгоритмов);

- 3) гарантированное время доставки пакетов;

- 4) максимальная пропускная способность сети;

- 5) устойчивость к блокировкам (дедлокам, лайвлокам);

- 6) пропускная способность;

- 7) загруженность буферов;

- 8) энергопотребление.

Ввиду большого разнообразия входных и выходных характеристик, определенная высокоуровневая модель может не иметь возможности расчета некоторых параметров. Тогда разработчик вынужден использовать для высокоуровневого моделирования несколько моделей, что увеличивает время моделирования, т.к. каких-либо инструментов позволяющих провести совместное моделирование СтнК несколькими моделями в рамках единой САПР не существует.

Низкоуровневое моделирование является более тщательной проверкой выходных характеристик СтнК, чем высокоуровневое моделирование и позволяет оценить:

- 1) затраты аппаратных ресурсов;

- 2) более точно, чем при высокоуровневом моделировании, пропускную способность (и другие высокоуровневые показатели);

- 3) наличие ошибок при маршрутизации.

Несмотря на то, что входные параметры СтнК определяются на этапе проектирования и являются одинаковыми для низкоуровневого и высокоуровневого моделирования, при исследовании не было найдено САПР, которая способна формировать задания для низкоуровневого этапа моделирования, основываясь на данных, введенных разработчиком для высокоуровневого этапа моделирования.

Этап прототипирования на программируемых логических интегральных схемах (ПЛИС) либо косимуляция помогает:

- 1) оценить аппаратные ресурсы сети;

- 2) оценить частоту работы сети;

- 3) определить работоспособность СтнК (нагрузочное тестирование).

Этап производства является финальным этапом, после которого СтнК реализуется на ПЛИС или производится в виде заказной микросхемы.

Данная работа относится к этапу высокоуровневого моделирования. На этом этапе с помощью специальных высокоуровневых моделей, по выбранным на этапе проектирования характеристикам и параметрам, производится подсчет выходных характеристик той или иной сети.

Высокоуровневое моделирование является важным этапом проектирования СтнК, а цена опибки на этом этапе очень высока, поскольку приводит к избыточному проведению низкоуровневого моделирования, которое на несколько порядков более затратно по времени, чем высокоуровневое моделирование. Например, из работы [10] следует, что высокоуровневое моделирование сети на 100 узлов с помощью модели OCNS (On-Chip Network Simulator) [18] занимает несколько минут, в то время как низкоуровневое моделирование той же сети с использованием Netmaker [19] — несколько дней.

# 4. Анализ разнообразия высокоуровневых моделей сетей на кристалле

Теоретические основы СтнК за последние десятилетия развивается очень интенсивно. Если ранее ключевыми были книги Axel Jantsch [20], Luca Benini [21], William James Dally [22], а моделей СтнК в открытом доступе были единицы [19], то сейчас количество публикаций и открытых разработок по тематике проектирования СтнК стало больше. В результате современному исследователю становится достаточно проблематично ориентироваться в различных идеях и подходах, предлагаемых другими авторами. При этом обзорных работ, где были бы собраны в сжатом и структурированном виде современные достижения в СтнК довольно мало. Есть ряд университетских курсов [23] и статей [24,25], дающих общий обзор тематики СтнК. Подробных обзоров из каких-то отдельных областей проектирования СтнК, как, например, это сделано в статье [26] в виде классификации алгоритмов маршрутизации,

также мало. Это касается и попыток классификации высокоуровневых моделей СтнК, которая представлена в работе [16]. Поэтому требуются проведение обзора и классификации подходов, используемых на этапах проектирования СтнК.

Для того, чтобы подготовить обзор в области высокоуровневого моделирования СтнК, было исследовано более 100 моделей. В основном были рассмотрены модели собранные в источнике [17]. В нем авторы представили результаты исследования в виде таблицы, что позволило в одном месте в компактном и структурированном виде собрать информацию по предметной области высокоуровневых моделей СтнК.

Проведенный обзор наиболее известных высокоуровневых моделей СтнК показал, что существуют различные модели, которые в основном решают частные задачи, нет универсальных моделей, все они не стандартизированы и зачастую не совместимы друг с другом. Для того, чтобы провести моделирование СтнК с собственной комбинацией параметров топологии, маршрутизации, метода контроля и генерации трафика, арбитража и т.д., необходимо создавать собственную модель или дорабатывать существующую. При этом практически отсутствуют средства автоматизации моделирования, которые бы облегчили обработку результатов моделирования и их верификации, проведение множественного запуска модели с различными параметрами и так далее. Нет средств интеграции моделей между собой. Такое состояние проблемной области определяет необходимость разработки САПР, которая бы позволила решить обозначенные проблемы.

# 5. Разработка архитектуры САПР для высокоуровневого моделирования СтнК

### 5.1 Архитектура САПР

Каждая модель СтнК имеет свой набор входных параметров и выходных характеристик. Когда требуется найти множество характеристик, для расчета которых нужно задействовать несколько моделей, разработчику приходится формировать задание на моделирование для каждой модели СтнК по отдельности, а затем собирать результаты моделирования вместе. Это увеличивает временные затраты на высокоуровневое моделирование, а также усложняет анализ полученных результатов и их передачу на следующий этап проектирования СтнК.

В разрабатываемую САПР для моделирования могут быть включены различные модели, благодаря чему, при получении набора параметров САПР может автоматически распределять эти параметры между моделями. Далее рассчитанные характеристики собираются и обрабатываются САПР, и пользователь получает единый подробный отчет. Таким образом можно упростить и автоматизировать процесс исследований характеристик СтнК и расширить список входных параметров и оцениваемых характеристик. Кроме того, можно сократить количество ошибок при оценивании тех характеристик, которые генерируются хотя бы двумя моделями, так как имеется возможность сравнения выходных характеристик обеих моделей.

Для разработки САПР требуется обеспечить:

- 1) синтез конфигурационных файлов для высокоуровневых моделей;

- 2) анализ задания пользователя на моделирование и оптимизацию расчетов;

- 3) синтез отчета с рассчитанными характеристиками;

- 4) анализ и хранение полученных результатов.

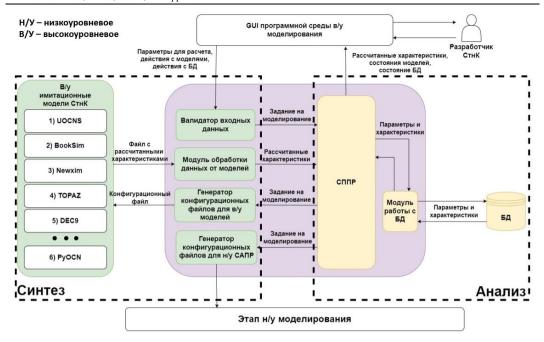

Для реализации САПР предлагается использовать архитектуру, изображенную на рис. 3. Архитектура состоит из ядра САПР, которое выделено сиреневым цветом, GUI для взаимодействия с пользователем, базы данных с результатами моделирования и подключаемых к ядру высокоуровневых имитационных моделей. Данные высокоуровневой модели являются разнородными и набор их неограничен.

Puc. 3. Архитектура разработанной САПР. Fig. 3. Architecture of the CAD developed.

Рассмотрим подробнее предлагаемую архитектуру САПР. Архитектура САПР логически разделена на этапы синтеза и анализа. Блок синтеза состоит из валидатора входных данных, генератора конфигурационных файлов для низкоуровневой САПР, модуля обработки получаемых от моделей данных, генератора конфигурационных файлов для высокоуровневых моделей и подключаемых моделей. Блок анализа состоит из системы поддержки принятия решений (СППР) и модуля работы с базой данных (БД).

После ввода пользователем задания, системой производится валидация входных данных и оценка задания СППР. СППР позволяет оценить производилось ли моделирование СтнК данной конфигурации ранее. Если проводилось, то система передает результаты моделирования из базы данных пользователю, если нет, то система помогает пользователю выбрать необходимые методы и высокоуровневые модели для проведения моделирования. Взаимодействие ядра САПР с моделями осуществляется путем передачи конфигурационного файла моделям и файла с рассчитанными характеристиками от модели ядру САПР. За генерацию конфигурационного файла и обработку данных, полученных от модели, отвечают два специализированных блока в ядре САПР.

Также стоит отметить, что, при необходимости, САПР способна сконфигурировать задание на низкоуровневое моделирование для передачи на следующий этап проектирования СтнК.

# 5.2 Клиент-серверная архитектура САПР

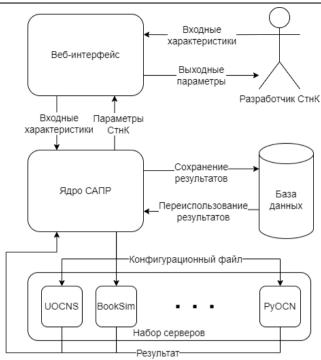

Для повышения эффективности и удобства работы с САПР, целесообразно перевести ее на клиент-серверную архитектуру, которая приведена на рис. 4. В предложенной архитектуре САПР представляет собой распределенную систему с веб-интерфейсом, ядром САПР, базой данных результатов моделирований и моделями СтнК.

Такая архитектура позволяет разработчику СтнК взаимодействовать с системой удаленно через веб-интерфейс. Разработчик вводит необходимые характеристики в веб-интерфейс. Далее, ядро САПР принимает входные характеристики и выполняет ряд задач, включая генерацию конфигурационных файлов для запуска моделей. Высокоуровневые модели могут 140

Puc. 4. Клиент-серверная архитектура САПР. Fig. 4. Client-server CAD architecture.

находиться на отдельных высокопроизводительных серверах. После формирования задания ядро проверяет наличие аналогичных расчетов в базе данных. Если подобное моделирование уже проводилось ранее, ядро САПР запрашивает результаты из базы данных, избегая повторных вычислений. В случае, если заданная конфигурация моделируется впервые, система запускает соответствующую модель на сервере, используя сгенерированный конфигурационный файл. По завершении расчетов результаты работы моделей собираются и агрегируются ядром САПР. Результаты индивидуальных запусков моделей сохраняются в базе данных, и выводятся пользователю через веб-интерфейс. Клиент-серверный подход к организации САПР позволяет реализовать многопользовательскую работу, делая возможным одновременное взаимодействие с САПР нескольких разработчиков через удаленный доступ. распределенной применения Благодаря архитектуре возможности производительных серверов, клиент-серверная архитектура САПР позволит значительно ускорить процесс моделирования СтнК. Также можно применить кеширование результатов работы моделей всех пользователей, которое сократит количество повторных вычислений и тем самым уменьшит время расчета параметров СтнК. Модульная архитектура и централизованное хранение результатов в базе данных позволяют улучшить целостность хранимых данных и обеспечивают возможность масштабирования системы для поддержки новых серверов и моделей по мере необходимости.

# 5.3 Удаленный маршрут проектирования СтнК

Рассмотрим более подробно типовую схему проектирования СтнК (рис. 2). Все этапы из данной схемы, кроме производства, можно реализовать удаленно, используя специализированные инструменты. Этапы составления технического задания и предварительного проектирования могут быть выполнены на компьютере разработчика.

Этапы высокоуровневого и низкоуровневого моделирования, хотя и могут быть выполнены на компьютере разработчика, требуют больших вычислительных затрат. Предложенная схема удаленного стенда для высокоуровневого моделирования СтнК позволяет решить проблему со слабыми вычислительными мощностями у пользователя. Такая схема также позволяет безопасно сохранять большое количество результатов проведенных пользователями моделирований (например, с помощью системы облачного хранения Synology Drive). Данную базу можно использовать для прогнозирования результатов расчетов или выводить пользователю результаты без необходимости запуска симулятора (если они уже есть в базе). Подобную архитектуру можно применить и для этапа низкоуровневого моделирования.

Этап прототипирования и симуляции можно проводить на стендах для удаленной работы со специализированным оборудованием. Например, осуществлять прототипирование разработанной СтнК на удаленных стендах для работы с платами ПЛИС [27,28]. Также существует подход, при котором можно разделить реализацию СтнК на несколько ПЛИС [29,30], что позволит выполнять прототипирование СтнК с большим количеством ядер.

Таким образом маршрут проектирования СтнК может быть полностью удаленным, включая моделирование СтнК на мощных вычислительных ресурсах с их дальнейший косимуляцией и прототипированием на удаленных стендах.

#### 6 Заключение

В статье проведен анализ классического цикла проектирования СтнК, выделены его основные этапы, представлена схема с этапами проектирования. Предложена архитектура САПР для моделирования СтнК, а также описана архитектура клиент-серверной реализации САПР, которая позволит выполнять моделирование СтнК удаленно. Предложен маршрут удаленного проектирования СтнК с возможностью высокоуровневого моделирования, косимуляции и прототипирования.

## Список литературы / References

- [1]. Shalf J. The future of computing beyond Moore's Law // Philos. Trans. R. Soc. A. The Royal Society Publishing, 2020, vol. 378, No 2166, p. 20190061.

- [2]. Shan Z. et al. Object Detection Based On Multi-Process // 2022 IEEE International Conference on Networking, Sensing and Control (ICNSC). IEEE, 2022, pp. 1–5.

- [3]. Paul K., Balakrishnan M., Lavenier D. Hardware acceleration of de Novo genome assembly // Int. J. Embed. Syst. Inderscience Publishers, 2017, vol. 9, No 1.

- [4]. Jia Z. et al. Dissecting the graphcore IPU architecture via microbenchmarking // arXiv Prepr. arXiv1912.03413. 2019.

- [5]. Moore S.K. Cerebras' New Monster AI Chip Adds 1.4 Trillion Transistors IEEE Spectrum // Cerebras' New Monster AI Chip Adds 1.4 Trillion Transistors. 2021. (online). https://spectrum.ieee.org/tech-talk/semiconductors/processors/cerebras-giant-ai-chip-now-has-a-trillions-more-transistors?utm\_source=techalert&utm\_medium=email&utm\_campaign=techalert-04-22-21&utm\_content=httpsspectrumieeeorgtechtalksemiconductorsprocessor, accessed 05.11.2024.

- [6]. He Y., Chen X. Survey and Comparison of Pipeline of Some RISC and CISC System Architectures // 2023 8th International Conference on Computer and Communication Systems (ICCCS). IEEE, 2023, pp. 785–790.

- [7]. Waterman A. et al. The RISC-V instruction set manual, volume I: User-level ISA, version 2.0 // EECS Dep. Univ. California, Berkeley, Tech. Rep. UCB/EECS-2014-54, 2014.

- [8]. Bjerregaard T., Mahadevan S. A survey of research and practices of Network-on-chip // ACM Comput. Surv. 2006, vol. 38, No 1, pp. 1–51. DOI: 10.1145/1132952.1132953.

- Sherwani N.A. Algorithms for VLSI physical design automation. Springer Science & Business Media, 2012.

- [10]. Romanov A., Ivannikov A. SystemC Language Usage as the Alternative to the HDL and High-level Modeling for NoC Simulation // Int. J. Embed. Real-Time Commun. Syst. 2018. DOI: 10.4018/IJERTCS.2018070102.

- [11]. Jain A. et al. Scalable design and synthesis of 3D mesh network on chip // Proceeding of International Conference on Intelligent Communication, Control and Devices: ICICCD 2016. Springer, 2017, pp. 661 – 666.

- [12]. Koohi S. et al. High-level modeling approach for analyzing the effects of traffic models on power and throughput in mesh-based NoCs // 21st international conference on VLSI design (VLSID 2008). IEEE, 2008, pp. 415–420.

- [13]. Czaja S.J., Nair S.N. Human factors engineering and systems design // Handb. Hum. factors Ergon. Wiley Online Library, 2012, pp. 38–56.

- [14]. Romanov A.Y. et al. Development of routing algorithms in networks-on-chip based on two-dimensional optimal circulant topologies // Heliyon. Elsevier Ltd, 2020, vol. 6, No 1, p. e03183. DOI: 10.1016/j.heliyon.2020.e03183.

- [15]. Romanov A.Y., Stepanov M.A. UOCNS-SE: Universal On-Chip Network Simulator Server (online). https://github.com/RomeoMe5/UOCNS-SE.

- [16]. Prilepko P.M., Romanov A., Lezhnev E.V. Modification of a High-Level NoCModel 2.0 for Modeling Networks-on-Chip with Circulant Topologies // Probl. Adv. micro- Nanoelectron. Syst. Dev. 2020. P. 23– 30. DOI: 10.31114/2078-7707-2020-4-23-30.

- [17]. Romanov A.Y., Opekunova A.A. NoC simulators comparison. 2020. https://github.com/RomeoMe5/NoC\_simulators\_comparison, accessed 05.11.2024.

- [18]. Romanov A.Y., Romanova I.I. Use of irregular topologies for the synthesis of networks-on-chip // 2015 IEEE 35th International Conference on Electronics and Nanotechnology (ELNANO). IEEE, 2015, pp. 445–449. DOI: 10.1109/ELNANO.2015.7146927.

- [19]. Romanov O., Lysenko O. The comparative analysis of the efficiency of regular and pseudo-optimal topologies of networks-on-chip based on Netmaker // 2012 Mediterranean Conference on Embedded Computing (MECO). IEEE, 2012, pp. 13–16.

- [20] Jantsch A., Tenhunen H. Networks on Chip // Networks on Chip / ed. Jantsch A., Tenhunen H. Boston, MA: Springer US, 2003. 312 p. DOI: 10.1007/b105353.

- [21]. De Micheli G., Benini L. Networks on Chips. First Edition / ed. Benini L. Morgan Kaufmann, 2006. 408 p.

- [22]. Dally W.J., Towles B.P. Principles and Practices of Interconnection Networks. Elsevier, 2003. 581 p.

- [23]. Balasubramonian R. CS6810 Lectures (online). Доступно по ссылке: https://www.youtube.com/playlist?list=PL8EC1756A7B1764F6, accessed 05.11.2024.

- [24]. Kakoee M.R., Bertacco V., Benini L. ReliNoC: A reliable network for priority-based on-chip communication // 2011 Design, Automation & Test in Europe. IEEE, 2011, pp. 1–6. DOI: 10.1109/DATE.2011.5763112.

- [25]. Bertozzi D. et al. NoC synthesis flow for customized domain specific multiprocessor systems-on-chip // IEEE Trans. Parallel Distrib. Syst. 2005, vol. 16, No 2, pp. 113–129. DOI: 10.1109/TPDS.2005.22.

- [26]. Gabis A.B., Koudil M. NoC routing protocols objective-based classification // J. Syst. Archit. Elsevier B.V., 2016, vol. 66–67, pp. 14–32. DOI: 10.1016/j.sysarc.2016.04.011.

- [27]. Lorens A., Petukhov G., Romanova I. FPGA-Based Asynchronous Remote Laboratory for Online Learning // 2022 International Russian Automation Conference (RusAutoCon). IEEE, 2022, pp. 623–627. DOI: 10.1109/RusAutoCon54946.2022.9896325.

- [28]. Измайлова Л.Г., Белоруков А.М., Романов А.Ю. Дистанционный стенд для синхронной работы с оборудованием на основе ПЛИС // Проблемы разработки перспективных микро- и наноэлектронных систем. 2022, vol. 4, pp. 117–121.

- [29]. Romashikhin M.Y., Romanova I.I. Parallel Calculation of π in NoCs Using a Remote Testbed // 2024 International Conference on Industrial Engineering, Applications and Manufacturing (ICIEAM). IEEE, 2024, pp. 996–1000. DOI: 10.1109/ICIEAM60818.2024.10553762.

- [30]. Romanov A., Lerner A., Amerikanov A. Cycle-accurate multi-FPGA platform for accelerated emulation of large on-chip networks // The Journal of Supercomputing. 2024, No 80, pp. 22462–22478. DOI: 10.1007/s11227-024-06306-3.

# Информация об авторах / Information about authors

Александр Александрович АМЕРИКАНОВ – кандидат технических наук, доцент национального исследовательского университета «Высшая школа экономики». Сфера

научных интересов: разработка САПР, разработка логических устройств, ПЛИС, сети на кристалле.

Aleksandr Aleksandrovich AMERIKANOV – Cand. Sci (Tech.), Associate Professor at the HSE University. Research interests: CAD development, development of logic devices, FPGA, networks-on-chip.

Лариса Геннадьевна ЕВТУШЕНКО — ассистент национального исследовательского университета «Высшая школа экономики». Сфера научных интересов: разработка логических устройств, ПЛИС.

Larisa Genadevna EVTUSHENKO – Assistant lecturer at the HSE University. Research interests: development of logic devices, FPGA.

Владимир Викторович ЗУНИН – старший преподаватель национального исследовательского университета «Высшая школа экономики». Сфера научных интересов: разработка САПР, разработка логических устройств, ПЛИС.

Vladimir Victorovich ZUNIN – Senior Lecturer at the HSE University. Research interests: CAD development, development of logic devices, FPGA.

Владимир Максимович ВИНАРСКИЙ – студент национального исследовательского университета «Высшая школа экономики». Сфера научных интересов: системы на кристалле, ПЛИС, машинное обучение.

Vladimir Maksimovich VINARSKII – Student at the HSE University. Research interests: SoC, FPGA, machine learning.