### Модифицированные коды с суммированием взвешенных переходов в системах функционального контроля комбинационных схем

<sup>1</sup> Д.В. Ефанов < TrES-4b@yandex.ru>

В.В. Сапожников < port.at.pgups@gmail.com>

Вл.В. Сапожников < at.pgups@gmail.com>

<sup>1</sup> Петербургский государственный университет путей сообщения Императора Александра I,

190031, Россия, г. Санкт-Петербург, Московский пр., д. 9

Предложен способ построения модифицированных суммированием взвешенных переходов между разрядами в информационных векторах, занимающими соседние позиции в информационных векторах. Новые коды с суммированием имеют такое же количество контрольных разрядов, как и классические коды Бергера, однако обнаруживают большее количество ошибок в информационных векторах. Модифицированные коды с суммированием взвешенных переходов по сравнению с кодами Бергера также имеют улучшенные характеристики обнаружения ошибок в области малой кратности. Кроме того, для некоторых значений длин информационных векторов могут быть построены коды с обнаружением любых двукратных и любых трехкратных ошибок. Авторами разработан способ синтеза систем функционального контроля комбинационных схем, основанный на анализе топологии объекта диагностирования с выделением групп контролепригодных выходов с учетом свойств обнаружения ошибок модифицированными кодами с суммированием взвешенных переходов. Сформирован алгоритм синтеза системы функционального контроля.

**Ключевые слова:** система функционального контроля; комбинационная схема; код Бергера; код с суммированием взвешенных переходов; обнаружение двукратных ошибок; обнаружение трехкратных ошибок.

**DOI:** 10.15514/ISPRAS-2017-29(5)-3

**Для цитирования:** Сапожников В.В., Сапожников Вл.В., Ефанов Д.В. Модифицированные коды с суммированием взвешенных переходов в системах функционального контроля комбинационных схем. Труды ИСП РАН, том 29, вып. 5, 2017 г., стр. 39-60. DOI: 10.15514/ISPRAS-2017-29(5)-3

#### 1. Введение

При построении надежных дискретных систем часто используются методы обнаружения отказов в процессе их функционирования, в частности, самопроверяемые схемы встроенного контроля (системы функционального контроля) [1 — 4]. Методы синтеза систем функционального контроля базируются на применении помехоустойчивого кодирования и, непосредственно, кодов, ориентированных на обнаружение ошибок. К таким кодам относятся равномерные блочные коды, включающие в себя большой класс кодов с суммированием (кодов Бергера и их модификаций [5 — 8]), а также неразделимые равновесные коды [9, 10].

Универсальным подходом при синтезе систем функционального контроля является использование разделимых кодов с суммированием, или (m,k)-кодов  $(m\ u\ k-$  длины информационных и контрольных векторов) [11-14]. Свойства (m,k)-кодов по обнаружению ошибок в информационных векторах определяют характеристики обнаружения ошибок на выходах объектов диагностирования в системах функционального контроля. Сложность же функций, описывающих разряды контрольных векторов (m,k)-кодов, напрямую связана со сложностью контрольного оборудования в системе диагностирования.

При синтезе системы диагностирования решается задача наилучшего покрытия неисправностей в объекте диагностирования. Наиболее популярной является классическая модель одиночных константных неисправностей выходов внутренних логических элементов (stuck-at fault) [1-4]. В системах функционального контроля реальных дискретных устройств должно быть обеспечено обнаружение любых неисправностей из заданного класса. Для решения этой задачи с учетом наименьших аппаратурных затрат используют свойства обнаружения ошибок (m,k)-кодами, а также различные виды функциональной зависимости между выходами объекта диагностирования [15-20].

### 2. Модифицированные коды с суммированием взвешенных переходов

Разделимые блочные коды для систем функционального контроля строятся по различным правилам, предполагающим операции суммирования как единичных информационных разрядов, так и взвешенных разрядов или переходов между разрядами, занимающими соседние позиции в информационных векторах [2, 5-8, 21].

Исследования способов модификации классических кодов с суммированием показали, что класс кодов с эффективным обнаружением ошибок в информационных векторах, в том числе, в области ошибок малой кратностью, может быть получен с использованием следующего способа построения.

<u>Алгоритм 1.</u> Последовательность построения модифицированного кода с суммированием взвешенных переходов:

- 1. Переходам между разрядами, занимающими соседние позиции в информационных векторах, приписываются весовые коэффициенты из натурального ряда чисел, начиная с перехода между младшими разрядами:  $[w_{m,m-1}, w_{m-1,m-2}, ..., w_2, w_1] = [m-1, m-2, ..., 2, 1].$

- 2. Устанавливается значение модуля  $M = 2^{\lceil \log_2(m+1)

ceil 1}$  .

- 3. Подсчитывается сумма весовых коэффициентов активных переходов:

$$W = \sum_{i=1}^{i=m-1} w_{i+1,i} (f_{i+1} \oplus f_i), \tag{1}$$

где  $f_i$  — значение i-го разряда в информационном векторе.

- 4. Определяется наименьший неотрицательный вычет числа W по модулю M:  $W_M = W \pmod{M}$ .

- 5. Подсчитывается специальный поправочный коэффициент α, как сумма по модулю два значений заранее выбранных информационных разрядов.

- 6. Вычисляется модифицированный вес информационного вектора:

$$V = W_M \pmod{M} + \alpha M. \tag{2}$$

7. Число V представляется в двоичном виде и записывается в разряды контрольного вектора.

Получаемый по алгоритму 1 код обозначим как RWT(m,k)-код, отдельно указывая формулу подсчета поправочного коэффициента  $\alpha$ . Следует отметить, что в [22] приведен способ построения одного из RWT(m,k)-кодов, в котором предполагается, что существует только единственный способ модификации: путем вычисления поправочного коэффициента по формуле  $\alpha = f_{m-k} \oplus \ldots \oplus f_{m-1} \oplus f_m$ .

Действия алгоритма 1 иллюстрируются в табл. 1 при построении RWT(4,3)-кода с поправочным коэффициентом, вычисляемым по формуле  $\alpha=f_3\oplus f_4$ .

При построении RWT(4,3)-кода с  $\alpha = f_3 \oplus f_4$  информационные векторы, имеющие равноудаленное расположение от центра таблицы задания кода (см. табл. 1), имеют одно и то же значение модифицированного веса V. Кроме того, в первой половине таблицы, благодаря поправочному коэффициенту, присутствуют по одному разу все веса из множества  $V \in \{0,1,...,7\}$ . Это обуславливает равномерное распределение всех информационных векторов между всеми контрольными векторами (табл. 2) и, что важнее, наличие в векторов с контрольной группе информационных d=m. Таким образом, необнаруживаемых расстоянием В классе рассматриваемым кодом ошибок находятся только четырехкратные ошибки в информационных векторах. Ошибки же с кратностями  $d \le 3$  данным кодом обнаруживаются.

Табл. 1. Кодовые слова RWT(4,3)-кода с  $\alpha = f_3 \oplus f_4$

Table 1. Code word of RWT(4,3)-code with  $\alpha = f_3 \oplus f_4$

| Десятичный                               |                          | ачения<br>формаі<br>вект                       | ционн |                         |   |         |   | Значения разрядов контрольного вектора |    |    |                       |

|------------------------------------------|--------------------------|------------------------------------------------|-------|-------------------------|---|---------|---|----------------------------------------|----|----|-----------------------|

| эквивалент<br>информационного<br>вектора | $f_4$ Become $w_{4,3}=3$ | f <sub>3</sub> вые коз перех 3 w <sub>3,</sub> | кодов | $f_1$ иенты $w_{2,1}=1$ | W | W(mod4) | α | V                                      | 83 | 82 | <i>g</i> <sub>1</sub> |

| 0                                        | 0                        | 0                                              | 0     | 0                       | 0 | 0       | 0 | 0                                      | 0  | 0  | 0                     |

| 1                                        | 0                        | 0                                              | 0     | 1                       | 1 | 1       | 0 | 1                                      | 0  | 0  | 1                     |

| 2                                        | 0                        | 0                                              | 1     | 0                       | 3 | 3       | 0 | 3                                      | 0  | 1  | 1                     |

| 3                                        | 0                        | 0                                              | 1     | 1                       | 2 | 2       | 0 | 2                                      | 0  | 1  | 0                     |

| 4                                        | 0                        | 1                                              | 0     | 0                       | 5 | 1       | 1 | 5                                      | 1  | 0  | 1                     |

| 5                                        | 0                        | 1                                              | 0     | 1                       | 6 | 2       | 1 | 6                                      | 1  | 1  | 0                     |

| 6                                        | 0                        | 1                                              | 1     | 0                       | 4 | 0       | 1 | 4                                      | 1  | 0  | 0                     |

| 7                                        | 0                        | 1                                              | 1     | 1                       | 3 | 3       | 1 | 7                                      | 1  | 1  | 1                     |

| 8                                        | 1                        | 0                                              | 0     | 0                       | 3 | 3       | 1 | 7                                      | 1  | 1  | 1                     |

| 9                                        | 1                        | 0                                              | 0     | 1                       | 4 | 0       | 1 | 4                                      | 1  | 0  | 0                     |

| 10                                       | 1                        | 0                                              | 1     | 0                       | 6 | 2       | 1 | 6                                      | 1  | 1  | 0                     |

| 11                                       | 1                        | 0                                              | 1     | 1                       | 5 | 1       | 1 | 5                                      | 1  | 0  | 1                     |

| 12                                       | 1                        | 1                                              | 0     | 0                       | 2 | 2       | 0 | 2                                      | 0  | 1  | 0                     |

| 13                                       | 1                        | 1                                              | 0     | 1                       | 3 | 3       | 0 | 3                                      | 0  | 1  | 1                     |

| 14                                       | 1                        | 1                                              | 1     | 0                       | 1 | 1       | 0 | 1                                      | 0  | 0  | 1                     |

| 15                                       | 1                        | 1                                              | 1     | 1                       | 0 | 0       | 0 | 0                                      | 0  | 0  | 0                     |

Табл. 2. Распределение информационных векторов RWT(4,3)-кода на контрольные группы

Table 2. Data vectors of RWT(4,3)-code distribution on check groups

| V   |                                 |   |   |   |   |   |   |  |  |  |

|-----|---------------------------------|---|---|---|---|---|---|--|--|--|

| 0   | 1                               | 2 | 3 | 4 | 5 | 6 | 7 |  |  |  |

|     | Контрольные векторы             |   |   |   |   |   |   |  |  |  |

| 000 | 000 001 010 011 100 101 110 111 |   |   |   |   |   |   |  |  |  |

|     | Информационные векторы          |   |   |   |   |   |   |  |  |  |

Ефанов Д.В., Сапожников В.В., Сапожников Вл.В. Модифицированные коды с суммированием взвешенных переходов в системах функционального контроля комбинационных схем. *Труды ИСП РАН*, том 29, вып. 5, 2017 г., стр. 39-60

| 0000 | 0001 | 0011 | 0010 | 0110 | 0100 | 0101 | 0111 |

|------|------|------|------|------|------|------|------|

| 1111 | 1110 | 1100 | 1101 | 1001 | 1011 | 1010 | 1000 |

Исследования показывают, что характеристики обнаружения ошибок модифицированными кодами с суммированием взвешенных переходов напрямую определяются способом вычисления поправочного коэффициента  $\alpha$ . Например, в табл. 3 даются распределения необнаруживаемых ошибок по видам и кратностям для семейства RWT(4,3)-кодов с всевозможными способами подсчета поправочного коэффициента. В каждой клетке таблицы указаны общее количество необнаруживаемых ошибок, а также три числа через косую черту — число монотонных, симметричных и асимметричных необнаруживаемых ошибок.

Табл. 3. Характеристики обнаружения ошибок различными RWT(4,3)-кодами Table 3. Error-detection characteristics by different RWT(4,3)-code

| Формула поправочного                            | Общее количество необнаруживаемых | Распределение необнаруживаемых ошибок по кратностям <i>d</i> |             |   |       |  |  |

|-------------------------------------------------|-----------------------------------|--------------------------------------------------------------|-------------|---|-------|--|--|

| коэффициента α                                  | ошибок                            | 1                                                            | 2           | 3 | 4     |  |  |

| $\alpha = 0$ ,                                  | 48                                | 0                                                            | 32          | 0 | 16    |  |  |

| $\alpha = f_1 \oplus f_2 \oplus f_3 \oplus f_4$ | 18 / 22 / 8                       |                                                              | 16 / 16 / 0 | Ŭ | 2/6/8 |  |  |

| $\alpha = f_1 \oplus f_3$ ,                     |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_2 \oplus f_3$ ,                     | 32                                | 0                                                            | 16          | 0 | 16    |  |  |

| $\alpha = f_1 \oplus f_4$ ,                     | 10 / 14 / 8                       |                                                              | 8/8/0       |   | 2/6/8 |  |  |

| $\alpha = f_2 \oplus f_4$                       |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_1$ ,                                |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_2$ ,                                |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_3$ ,                                |                                   | 0                                                            | 16<br>8/8/0 | 0 |       |  |  |

| $\alpha = f_4$ ,                                | 16                                |                                                              |             |   | 0     |  |  |

| $\alpha = f_1 \oplus f_2 \oplus f_3,$           | 8/8/0                             |                                                              |             |   | · ·   |  |  |

| $\alpha = f_1 \oplus f_2 \oplus f_4,$           |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_1 \oplus f_3 \oplus f_4,$           |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_2 \oplus f_3 \oplus f_4$            |                                   |                                                              |             |   |       |  |  |

| $\alpha = f_1 \oplus f_2$ ,                     | 16                                | 0                                                            | 0           | 0 | 16    |  |  |

| $\alpha = f_3 \oplus f_4$                       | 2/6/8                             | J                                                            | J           | U | 2/6/8 |  |  |

В табл. 4 приводятся рассчитанные значения долей необнаруживаемых ошибок кратностью d от общего количества ошибок данной кратностью (величин  $\beta_d$ , %) для различных кодов с суммированием с длиной информационного вектора m=4. В таблице представлены данные для семейства RWT(4,3)-кодов с различными способами подсчета поправочного

коэффициента  $\alpha$ , а также величины для классического кода Бергера (S(4,3)-кода) [23], модифицированного кода Бергера (RS(4,3)-кода) [24], а также модульных кодов с суммированием взвешенных разрядов (WSM(4,3)-кода) и переходов (WTM(4,3)-кода) [25]. Некоторые из разработанных RWT(4,3)-кодов имеют улучшенные характеристики обнаружения ошибок по сравнению с известными кодами с суммированием.

Табл. 4. Обнаружение ошибок кодами с суммированием при m=4 Table 4. Error-detection by sum codes with m=4

|                  | Формула Формула                                                                                                                                                                                                        |                     |           | β <sub>d</sub> , % |        |        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|--------------------|--------|--------|

| Код              | поправочного<br>коэффициента α                                                                                                                                                                                         | 1                   | 2         | 3                  | 4      | 1 ÷ 4  |

| 1                | Модифицированный код с суммир                                                                                                                                                                                          | ованием<br>Пованием | і взвешен | ных пере           | ехолов |        |

| $\alpha = 0$ .   |                                                                                                                                                                                                                        |                     |           |                    | подов  |        |

| <i>RWT</i> (4,3) | $\alpha = f_1 \oplus f_2 \oplus f_3 \oplus f_4$                                                                                                                                                                        | 0                   | 33,333    | 0                  | 100    | 20     |

| RWT(4,3)         | $\alpha = f_1 \oplus f_3, \ \alpha = f_2 \oplus f_3,$<br>$\alpha = f_1 \oplus f_4, \ \alpha = f_2 \oplus f_4$                                                                                                          | 0                   | 16,667    | 0                  | 100    | 13,333 |

| RWT(4,3)         | $\alpha = f_1, \ \alpha = f_2, \ \alpha = f_3,$ $\alpha = f_4, \ \alpha = f_1 \oplus f_2 \oplus f_3,$ $\alpha = f_1 \oplus f_2 \oplus f_4,$ $\alpha = f_1 \oplus f_3 \oplus f_4,$ $\alpha = f_2 \oplus f_3 \oplus f_4$ | 0                   | 16,667    | 0                  | 0      | 6,667  |

| RWT(4,3)         | $\alpha = f_1 \oplus f_2, \ \alpha = f_3 \oplus f_4$                                                                                                                                                                   | 0                   | 0         | 0                  | 100    | 6,667  |

|                  | Код Бе                                                                                                                                                                                                                 | ргера               |           |                    |        |        |

| S(4,3)           | _                                                                                                                                                                                                                      | 0                   | 50        | 0                  | 37,5   | 22,5   |

|                  | Другие модифицированны                                                                                                                                                                                                 | е коды с            | суммиро   | ванием             |        |        |

| RS(4,3)          | $\alpha = f_1, \ \alpha = f_2, \ \alpha = f_3,$ $\alpha = f_4, \ \alpha = f_1 \oplus f_2 \oplus f_3,$ $\alpha = f_1 \oplus f_2 \oplus f_4,$ $\alpha = f_1 \oplus f_3 \oplus f_4,$ $\alpha = f_2 \oplus f_3 \oplus f_4$ | 0                   | 25        | 0                  | 0      | 10     |

| RS(4,3)          | $\alpha = f_1 \oplus f_2, \ \alpha = f_3 \oplus f_4$<br>$\alpha = f_1 \oplus f_3, \ \alpha = f_2 \oplus f_3,$<br>$\alpha = f_1 \oplus f_4, \ \alpha = f_2 \oplus f_4$                                                  | 0                   | 16,667    | 0                  | 50     | 10     |

| WSM(4,3)         |                                                                                                                                                                                                                        | 0                   | 0         | 18,75              | 25     | 6,667  |

| <i>WTM</i> (4,3) | _                                                                                                                                                                                                                      | 0                   | 8,333     | 0                  | 100    | 10     |

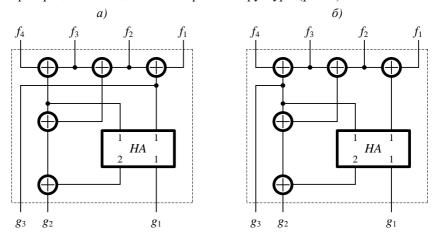

Среди всех RWT(4,3)-кодов выделяются два кода, поправочные коэффициенты которых вычисляются по формулам  $\alpha = f_1 \oplus f_2$  и  $\alpha = f_3 \oplus f_4$ . Данными кодами обнаруживаются любые ошибки с кратностями  $d \le 3$ . При этом генераторы данных кодов имеют простые структуры (рис. 1).

*Puc. 1.* Схемы генераторов *RWT*(4,3)-кодов: a) с  $\alpha = f_1 \oplus f_2$ ; б) с  $\alpha = f_3 \oplus f_4$  *Fig. 1. RWT*(4,3)-code generators circuits: a) with  $\alpha = f_1 \oplus f_2$ ; b) with  $\alpha = f_3 \oplus f_4$

# 3. Характеристики обнаружения ошибок модифицированными кодами с суммированием взвешенных переходов

К сожалению, с увеличением длины информационного вектора свойство обнаружения RWT(m,k)-кодами любых трехкратных ошибок в информационных векторах теряется. Однако модифицированные коды с суммированием взвешенных переходов остаются по характеристикам обнаружения ошибок различных кратностей более эффективными, чем рассмотренные выше коды с суммированием (см. табл. 4).

Исследования RWT(m,k)-кодов при различных длинах информационных векторов показали следующие важные особенности. Различные способы вычисления поправочного коэффициента  $\alpha$  дают различные по своим характеристикам RWT(m,k)-коды. Помехоустойчивые RWT(m,k)-коды могут быть построены при любых сочетаниях информационных разрядов в сумме поправочного коэффициента  $\alpha$  для любых значений длин информационных векторов за исключением  $m=2^q+1,\ q=1,2,\ldots$  Для построения помехоустойчивых RWT(m,k)-кодов при  $m=2^q+1,\ q=1,2,\ldots$ , необходимо, что в сумме поправочного коэффициента  $\alpha$  присутствовал старший

информационный разряд. Такая особенность модифицированных взвешенных кодов связана с тем, что при значении длины информационного вектора  $m = 2^{q} + 1$  значение модуля  $M = 2^{q}$  и старший разряд  $f_{m}$ , переход между которым и разрядом  $f_{m-1}$ , имеет весовой коэффициент, равный числу M, не контролируется разрядами контрольного вектора [26]. Для наделения RWT(m,k)-кода свойством помехоустойчивости в рассмотренном случае требуется контроль старшего разряда в сумме поправочного коэффициента. Следует также подчеркнуть, что RWT(m,k)-коды, для которых поправочный формулам  $\alpha = 0$ коэффициент вычисляется по И  $\alpha = f_1 \oplus f_2 \oplus ... \oplus f_{m-1} \oplus f_m$ эффективно используют старший не контрольный разряд, ввиду чего не обнаруживают большее количество ошибок, чем все остальные модифицированных коды с суммированием взвешенных переходов.

Дальнейшие исследования показали, что число кодов с различными характеристиками обнаружения ошибок гораздо меньше числа способов подсчета поправочного коэффициента. Например, в табл. 5 приведены характеристики обнаружения ошибок по кратностям всеми RWT(m,k)-кодами при  $m=5 \div 7$ , а в табл. 6-RWT(m,k)-кодами при m=8. При больших значениях длин информационных векторов число разнообразных RWT(m,k)-кодов является существенным. При этом для коэффициента  $\alpha$  для сокращения записи использовано следующее обозначение: коэффициент  $\alpha$  представлен в виде десятичного числа-эквивалента формулы подсчета (например, число 57 представляется в двоичном виде как  $< f_7 f_6 f_5 f_4 f_3 f_2 f_1 > = <0111001>$ , что означает использование при вычислении поправочного коэффициента формулы  $\alpha = f_1 \oplus f_4 \oplus f_5 \oplus f_6$ ).

Модифицированным кодам с суммированием взвешенных переходов присуща следующая закономерность. При четных значениях m RWT(m,k)-коды обнаруживают любые ошибки нечетной кратностью в информационных векторах. Это свойство характерно также любому коду с суммированием единичных информационных разрядов [8].

Отдельно следует упомянуть о модифицированных взвешенных кодах с обнаружением любых двукратных ошибок в информационных векторах. Такие коды строятся при m=4, 5 и 8. Из табл. 3 и 5 следует, что существует по два способа построения RWT(m,k)-кодов с обнаружением любых двукратных ошибок при значениях m=4 и m=5. При m=8 таких способов 16. Укажем десятичные эквиваленты поправочных коэффициентов для данных RWT(m,k)-кодов: (135, 165, 210, 240), (143, 173, 218, 248), (147, 177, 198, 228), (155, 185, 206, 236). В скобках выделены способы вычисления поправочных коэффициентов  $\alpha$  с абсолютно идентичными характеристиками обнаружения ошибок в информационных векторах.

При этом, что является важным для задач технической диагностики, некоторые способы вычисления поправочного коэффициента  $\alpha$  дают возможность построения таких RWT(m,k)-кодов, которые имеют минимально возможное общее количество необнаруживаемых ошибок при заданных значениях m и k [24].

*Табл. 5. Обнаружение ошибок RWT(5,3) и RWT(6,3)*

Table 5. Error-detection by RWT(5,3) and RWT(6,3) codes

| Способ вычисления поправочного                         | Чис         | ло необ | наруживае и значен |      | _    | тності | ью <i>d</i> |  |  |  |

|--------------------------------------------------------|-------------|---------|--------------------|------|------|--------|-------------|--|--|--|

| коэффициента α                                         | 2           | 3       | 4                  | 5    | 6    | 7      | 2 ÷ 7       |  |  |  |

|                                                        |             | m=5     |                    |      |      |        |             |  |  |  |

| 19, 28                                                 | 0           | 64      | 32                 | 0    |      |        | 96          |  |  |  |

| 17, 20                                                 | 0%          | 20%     | 20%                | 0%   |      |        | 9,68%       |  |  |  |

| 17, 18, 20, 23, 24, 27, 29, 30                         | 32          | 32      | 0                  | 32   |      |        | 96          |  |  |  |

| 17, 16, 20, 23, 24, 27, 29, 30                         | 10%         | 10%     | 0%                 | 100% |      |        | 9,68%       |  |  |  |

| 21, 22, 25, 26                                         | 32          | 32      | 32                 | 0    |      |        | 96          |  |  |  |

| 21, 22, 23, 20                                         | 10%         | 10%     | 20%                | 0%   |      |        | 9,68%       |  |  |  |

| 16.21                                                  | 64          | 0       | 32                 | 0    |      |        | 96          |  |  |  |

| 16, 31                                                 | 20%         | 0%      | 20%                | 0%   |      |        | 9,68%       |  |  |  |

|                                                        | <i>m</i> =6 |         |                    |      |      |        |             |  |  |  |

| 19, 28, 35, 44                                         | 128         | 0       | 320                | 0    | 0    |        | 448         |  |  |  |

| 17, 26, 33, 44                                         | 13,33%      | 0%      | 33,33%             | 0%   | 0%   |        | 11,11%      |  |  |  |

| 3, 12, 15, 17, 18, 20, 23, 24,                         | 192         | 0       | 192                | 0    | 64   |        | 448         |  |  |  |

| 27, 29, 30, 33, 34, 36, 39, 40, 43, 45, 46, 48, 51, 60 | 20%         | 0%      | 20%                | 0%   | 100% |        | 11,11%      |  |  |  |

| 7, 11, 13, 14, 21, 22, 25, 26,                         | 192         | 0       | 256                | 0    | 0    |        | 448         |  |  |  |

| 37, 38, 41, 42, 49, 50, 52, 56                         | 20%         | 0%      | 26,67%             | 0%   | 0%   |        | 11,11%      |  |  |  |

| 16, 31, 32, 47                                         | 256         | 0       | 192                | 0    | 0    |        | 448         |  |  |  |

| 10, 31, 32, 47                                         | 26,67%      | 0%      | 20%                | 0%   | 0%   |        | 11,11%      |  |  |  |

| 5, 6, 9, 10, 53, 54, 57, 58                            | 256         | 0       | 256                | 0    | 64   |        | 576         |  |  |  |

| 3, 0, 7, 10, 33, 34, 37, 36                            | 26,67%      | 0%      | 26,67%             | 0%   | 100% |        | 14,29%      |  |  |  |

| 1, 2, 4, 8, 55, 59, 61, 62                             | 320         | 0       | 128                | 0    | 0    |        | 448         |  |  |  |

| 1, 2, 4, 6, 33, 37, 61, 62                             | 33,33%      | 0%      | 13,33%             | 0%   | 0%   |        | 11,11%      |  |  |  |

| 0, 63                                                  | 448         | 0       | 448                | 0    | 64   |        | 960         |  |  |  |

| 0, 05                                                  | 46,67%      | 0%      | 46,67%             | 0%   | 100% |        | 23,81%      |  |  |  |

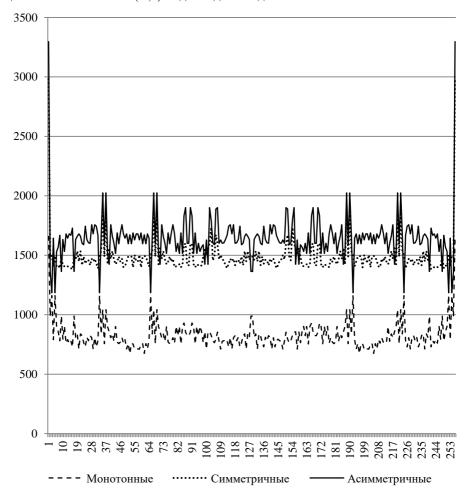

Что касается распределений ошибок по видам для RWT(m,k)-кодов, то оно также разнообразно для различных способов подсчета поправочного коэффициента. Например, на рис. 2 представлено распределение ошибок по видам для RWT(8,4)-кодов (по оси абсцисс расположены десятичные

эквиваленты формул подсчета поправочного коэффициента  $\alpha$ , а по оси ординат — количество необнаруживаемых ошибок данного вида). Распределения ошибок по видам симметричны относительно центральных значений десятичных эквивалентов поправочных коэффициентов при четных значениях m, при нечетных значениях данная закономерность нарушается. Для малых значений длин информационных векторов  $m \le 6$  более распространенными оказывают симметричные необнаруживаемые ошибки. При больших значениях m наименьшим является количество монотонных, затем симметричных и асимметричных ошибок в классе необнаруживаемых RWT(m,k)-кодами ошибок.

Табл. 6. Обнаружение ошибок RWT(7,3)-кодами Table 6. Error-detection by RWT(7,3)-codes

| Способ вычисления                                                                         | Число необнаруживаемых ошибок кратностью $d$ и значения величин $\beta_d$ |        |        |        |    |      |        |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------|--------|--------|----|------|--------|--|

| поправочного                                                                              | 2                                                                         |        |        |        |    | T =  | 2 7    |  |

| коэффициента α                                                                            | 2                                                                         | 3      | 4      | 5      | 6  | 7    | 2 ÷ 7  |  |

| 7, 11, 13, 14, 19, 28, 35,                                                                | 256                                                                       | 512    | 640    | 512    | 0  | 0    | 1920   |  |

| 44, 49, 50, 52, 56, 67, 76, 79, 112, 115, 124                                             | 9,52%                                                                     | 11,43% | 14,29% | 19,05% | 0% | 0%   | 11,81% |  |

| 3, 12, 15, 48, 51, 60, 71,                                                                | 256                                                                       | 640    | 640    | 256    | 0  | 128  | 1920   |  |

| 75, 77, 78, 83, 92, 99, 108, 113, 114, 116, 120                                           | 9,52%                                                                     | 14,29% | 14,29% | 9,52%  | 0% | 100% | 11,81% |  |

| 21, 22, 25, 26, 37, 38,                                                                   | 384                                                                       | 384    | 768    | 384    | 0  | 0    | 1920   |  |

| 41, 42                                                                                    | 14,29%                                                                    | 8,57%  | 17,14% | 14,29% | 0% | 0%   | 11,81% |  |

| 5, 6, 9, 10, 17, 18, 20,                                                                  | 384                                                                       | 512    | 512    | 384    | 0  | 128  | 1920   |  |

| 23, 24, 27, 29, 30, 33,<br>34, 36, 39, 40, 43, 45,<br>46, 53, 54, 57, 58                  | 14,29%                                                                    | 11,43% | 11,43% | 14,29% | 0% | 100% | 11,81% |  |

| 65, 66, 68, 72, 80, 95,                                                                   | 512                                                                       | 384    | 384    | 512    | 0  | 128  | 1920   |  |

| 96, 111, 119, 123, 125,<br>126                                                            | 19,05%                                                                    | 8,57%  | 8,57%  | 19,05% | 0% | 100% | 11,81% |  |

| 69, 70, 73, 74, 81, 82,                                                                   | 384                                                                       | 640    | 512    | 384    | 0  | 0    | 1920   |  |

| 84, 87, 88, 91, 93, 94,<br>97, 98, 100, 103, 104,<br>107, 109, 110, 117, 118,<br>121, 122 | 14,29%                                                                    | 14,29% | 11,43% | 14,29% | 0% | 0%   | 11,81% |  |

| 85, 86, 89, 90, 101, 102,                                                                 | 384                                                                       | 768    | 768    | 384    | 0  | 128  | 2432   |  |

| 105, 106                                                                                  | 14,29%                                                                    | 17,14% | 17,14% | 14,29% | 0% | 100% | 14,96% |  |

| 1, 2, 4, 8, 16, 31, 32, 47,                                                               | 512                                                                       | 768    | 384    | 256    | 0  | 0    | 1920   |  |

| 55, 59, 61, 62                                                                            | 19,05%                                                                    | 17,14% | 8,57%  | 9,52%  | 0% | 0%   | 11,81% |  |

| 64, 127                                                                                   | 768                                                                       | 0      | 1152   | 0      | 0  | 0    | 1920   |  |

| 04, 127                                                                                   | 28,57%                                                                    | 0%     | 25,71% | 0%     | 0% | 0%   | 11,81% |  |

| 0.63                                                                                      | 768                                                                       | 1152   | 1152   | 768    | 0  | 128  | 3968   |  |

| 0, 63                                                                                     | 28,57%                                                                    | 25,71% | 25,71% | 28,57% | 0% | 100% | 24,41% |  |

Подобные графики (см. рис. 2) позволяют определить диапазоны разбросов значений чисел необнаруживаемых кодами ошибок различных видов для целого семейства RWT(m,k)-кодов заданной длины.

Puc. 2. Распределение необнаруживаемых ошибок по видам для различных RWT(8,4)-кодов Fig. 2. Distribution of undetectable errors by types for different RWT(8,4)-codes

### 4. Понятие об r-независимых группах выходов комбинационных схем

RWT(m,k)-коды могут быть использованы при синтезе систем функционального контроля комбинационных логических схем. В особенности это касается кодов с обнаружением любых ошибок с кратностями  $d \le 3 - RWT(4,3)$ -кодов с  $\alpha = f_1 \oplus f_2$  и  $\alpha = f_3 \oplus f_4$ .

RWT(4,3)-коды могут быть эффективно использованы при организации контроля комбинационных схем по группам, содержащим по 4 выхода. Каждая такая группа должна удовлетворять одному условию — выходы группы не должны допускать одновременного искажения значений, то есть обладать независимостью относительно четырехкратных искажений. Сформулируем условия поиска логических элементов  $G_t$  комбинационных схем допускающих четырехкратные искажения.

Известны следующие положения [2, 11].

Определение 1. Подмножество выходов комбинационной схемы  $f_{i_1}, f_{i_2}, ..., f_{i_q}$  ( $f_{i_1}, f_{i_2}, ..., f_{i_q}$ ) (образует  $f_{i_1}, f_{i_2}, ..., f_{i_q}$ ) (образует  $f_{i_1}, f_{i_2}, ..., f_{i_q}$ ) если неисправность выхода любого логического элемента схемы искажает значения только одного выхода группы.

**Теорема 1.** Множество выходов комбинационной схемы  $\left\{f_{i_1}, f_{i_2}, ..., f_{i_q}\right\}$   $(i_1, i_2, ..., i_q \in \{1, 2, ..., n\}, \ n$  – число выходов схемы) образует  $\mathbf{H}^1$ -группу, если для каждой пары выходов  $\left\{f_{i_a}, f_{i_c}\right\}$   $(a, b \in \{1, 2, ..., q\})$  и для каждого логического элемента  $G_t$  выполняется условие:

$$\frac{\partial f_{i_a}}{\partial y_t} \frac{\partial f_{i_b}}{\partial y_t} = 0, \tag{3}$$

где  $f_{i_a}$  и  $f_{i_b}$  – функции, реализуемые на соответствующих выходах логической схемы;

$y_t$  – функция, реализуемая на выходе элемента  $G_t$ .

Используя понятие независимых выходов, введем понятие H'-группы выходов.

Определение 2. Множество выходов схемы  $\left\{f_{i_1}, f_{i_2}, ..., f_{i_q}\right\}$   $(i_1, i_2, ..., i_q \in \{1, 2, ..., n\})$  является r-независимой группой выходов (H<sup>r</sup>-группой), если неисправность выхода любого логического элемента схемы искажает значения не более r выходов группы.

**Теорема 2.** Множество выходов логической схемы

$$\left\{f_{i_1}, f_{i_2}, ..., f_{i_n}\right\}$$

( $q \ge r+1$ )

образует  $H^r$ -группу, если для каждого из  $C_q^{r+1}$  подмножеств из r+1 выходов и для каждого элемента логической схемы выполняется условие:

$$\frac{\partial f_{i_1}}{\partial y_t} \frac{\partial f_{i_2}}{\partial y_t} \cdot \dots \cdot \frac{\partial f_{i_{r+1}}}{\partial y_t} = 0. \tag{4}$$

**Доказательство.** Справедливость данного положения следует из того, что каждая производная в левой части выражения (4) определяет те входные наборы, на которых неисправность элемента с выходом  $y_t$  проявляется на соответствующем выходе, а произведение всех четырех производных определяет те входные наборы, на которых одновременно искажаются все четыре выхода. Если для каждого элемента условие (4) выполняется, значит, на множестве выходов ни при каких условиях не будут возникать искажения с кратностью  $d \ge r+1$ . **Доказательство завершено.**

При организации контроля логических устройств по группам r-независимых выходов требуется определить конкретное значение числа r. Это делается с учетом свойств обнаружения ошибок выбранным на этапе проектирования системы функционального контроля кодом:  $r=d_{\min}-1$ , где  $d_{\min}$  — минимальное расстояние Хэмминга для кодовых слов выбранного кода. Например, при использовании RWT(4,3)-кодов с  $\alpha=f_1\oplus f_2$  и  $\alpha=f_3\oplus f_4$   $d_{\min}=4$ , а значит, контроль схем может быть осуществлен на основе выделения  $H^3$ -групп выходов.

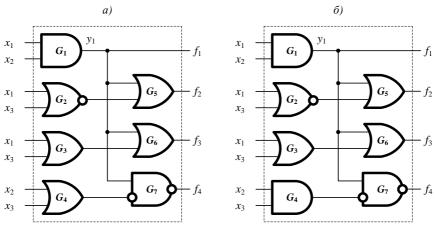

Для примера рассмотрим схемы, изображенные на рис. 3.

Четырехкратные искажения может вызывать только элемент  $G_1$ . Определим, является ли каждая из схем схемой с  $H^3$ -группой выходов. Для этого выпишем функции, реализуемые на выходах схем. Для схемы на рис. 3, а) имеем:

$$f_1 = y_1, \ f_2 = y_1 \lor \overline{x_1 \lor x_3}, \ f_3 = y_1 \lor x_1 \overline{x_2} x_3 \text{ if } f_4 = \overline{y_1 \overline{x_2} \lor x_3}.$$

Вычислим булевы производные для каждого из выходов:

$$\frac{\partial f_1}{\partial y_1} = (y_1 = 0) \oplus (y_1 = 1) = 1;$$

$$\frac{\partial f_2}{\partial y_1} = (y_1 = 0) \vee \overline{x_1 \vee x_3} \oplus (y_1 = 1) \vee \overline{x_1 \vee x_3} = x_1 \vee x_3;$$

$$\frac{\partial f_3}{\partial y_1} = (y_1 = 0) \vee x_1 \overline{x_2} x_3 \oplus (y_1 = 1) \vee x_1 \overline{x_2} x_3 = \overline{x_1} \vee x_2 \vee \overline{x_3};$$

Efanov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. Modified codes with weighted-transitions summation in concurrent error detection systems of combinational circuits. *Trudy ISP RAN/Proc. ISP RAS*, vol. 29, issue 5, 2017, pp. 39-60

$$\frac{\partial f_4}{\partial y_1} = \overline{(y_1 = 0)\overline{x_2 \vee x_3}} \oplus \overline{(y_1 = 1)\overline{x_2 \vee x_3}} = \overline{x_2}\overline{x_3};$$

Puc. 3. Комбинационные схемы: a) схема, выходы которой образуют 3-независимую группу; б) схема, выходы которой не образуют 3-независимую группу Fig 3. Combinational circuits: a) circuit with 3-independence outputs group; b) circuit without 3-independence outputs group

$$\frac{\partial f_1}{\partial y_1} \frac{\partial f_2}{\partial y_1} \frac{\partial f_3}{\partial y_1} \frac{\partial f_4}{\partial y_1} = 1 \cdot (x_1 \vee x_3) (\overline{x_1} \vee x_2 \vee \overline{x_3}) (\overline{x_2} \overline{x_3}) = 0.$$

Выводом из последнего выражения является то, что схема на рис. 3, а) является схемой с 3-независимыми выходами.

Для схемы на рис. 3, б) отличается только функция  $f_4$ :

$$f_4 = y_1 x_2 x_3.$$

Вычислим производную для данной функции по переменной  $y_1$ :

$$\frac{\partial f_4}{\partial y_1} = \overline{(y_1 = 0)\overline{x_2x_3}} \oplus \overline{(y_1 = 1)\overline{x_2x_3}} = \overline{x_2} \vee \overline{x_3};$$

$$\frac{\partial f_1}{\partial y_1} \frac{\partial f_2}{\partial y_1} \frac{\partial f_3}{\partial y_1} \frac{\partial f_4}{\partial y_1} = 1 \cdot (x_1 \vee x_3) (\overline{x_1} \vee x_2 \vee \overline{x_3}) (\overline{x_2} \vee \overline{x_3}) = \overline{x_1} \overline{x_2} x_3 \vee x_1 \overline{x_3}.$$

Схема на рис. 3, б) не является 3-независимой.

## 5. Алгоритм синтеза системы функционального контроля на основе выделения 3-независимых групп выходов

Сформируем алгоритм построения системы функционального контроля на основе выделения  $H^3$ -групп на множестве выходов контролируемой комбинационной схемы и контроле каждой из групп на основе RWT(4,3)-кода. Алгоритм 2. Последовательность построения системы функционального контроля:

- 1. Определяется множество  $Q^4$  логических элементов  $G_i$ , связанных путями с четырьмя и более выходами схемы.

- 2. Для каждого логического элемента  $G_i$  из подмножества  $\mathcal{Q}^4$  определяется подмножество выходов схемы  $G_i(f) = \left\{f_{i_1}, f_{i_2}, ..., f_{i_q}\right\}$ , с которыми он связан.

- 3. Определяется подмножество  $G^0(f)$  путем объединения всех подмножеств, полученных в п.2.

- 4. Рассматривается каждое подмножество  $G_i^4(f) \in G^0(f)$ , содержащее три выхода. Для него проверяется условие теоремы 2 относительно элементов  $G_i \in Q^4$ .

- 5. По результатам выполнения п.4 составляется множество  $W_z$  групп выходов  $G_i^4(f)$ , которые не являются  $H^3$ -группами.

- 6. Решается задача покрытия выходов схемы подмножествами  $G_i^4(f)$  3-независимых групп выходов с учетом минимального количества таких групп.

- 7. Каждая 3-независимая группа выходов схемы, полученная в п.6, контролируется на основе  $\mathit{RWT}(4,3)$ -кода (с  $\alpha = f_1 \oplus f_2$ , либо с  $\alpha = f_3 \oplus f_4$ ) строятся отдельные подсхемы контроля каждой группы выходов.

- 8. Если какие-либо выходы схемы не вошли в покрытие выходов подмножествами  $G_i^4(f)$ , для них реализуется подсхема контроля по методу дублирования.

- 9. Выходы подсхем контроля объединяются на входах самопроверяемого компаратора, реализуемого на основе стандартных модулей сжатия парафазных сигналов TRC [27].

Следует отметить, что при реализации шагов алгоритма 2 могут, в конечном итоге, остаться  $H^2$ -группы и  $H^1$ -группы выходов. Они также могут контролироваться на основе RWT(4,3)-кодов, однако эффективнее может оказаться применение для контроля  $H^2$ -групп кодов с обнаружением любых

одно- и двукратных ошибок [28 - 31] и для контроля  $H^1$ -групп выходов кодов паритета [32, 33].

#### 6. Заключение

Предложенный в статье класс модифицированных взвешенных кодов с суммированием переходов между разрядами, занимающими соседние позиции в информационных векторах, можно эффективно использовать в задачах технической диагностики дискретных систем. При этом при значении m=4 получены коды с обнаружением любых ошибок кратностью d≤3. Используя последние и выделяя во множестве выходов комбинационных схем группы 3-независимых выходов, можно строить системы функционального контроля с обнаружением любых одиночных константных неисправностей во внутренней структуре контролируемых объектов.

### Список литературы

- [1]. McCluskey E.J. Logic Design Principles: With Emphasis on Testable Semicustom Circuits. N.J.: Prentice Hall PTR, 1986, 549 p.

- [2]. Согомонян Е.С., Слабаков Е.В. Самопроверяемые устройства и отказоустойчивые системы. М.: Радио и связь, 1989, 207 с.

- [3]. Goessel M., Graf S. Error Detection Circuits. London: McGraw-Hill, 1994, 261 p.

- [4]. Mitra S., McCluskey E.J. Which Concurrent Error Detection Scheme to Choose? Proceedings of International Test Conference, 2000, USA, Atlantic City, NJ, 03-05 October 2000, pp. 985-994, doi: 10.1109/TEST.2000.894311.

- [5]. Berger J.M. A Note on Error Detection Codes for Asymmetric Channels. Information and Control, 1961, Vol. 4, Issue 1, pp. 68-73, doi: 10.1016/S0019-9958(61)80037-5.

- [6]. Piestrak S.J. Design of Self-Testing Checkers for Unidirectional Error Detecting Codes. Wrocław: Oficyna Wydawnicza Politechniki Wrocłavskiej, 1995, 111 p.

- [7]. Das D., Touba N.A. Synthesis of Circuits with Low-Cost Concurrent Error Detection Based on Bose-Lin Codes. Journal of Electronic Testing: Theory and Applications, 1999, Vol. 15, Issue 1-2, pp. 145-155, doi: 10.1023/A:1008344603814.

- [8]. Блюдов А.А., Ефанов Д.В., Сапожников В.В., Сапожников Вл.В. О кодах с суммированием единичных разрядов в системах функционального контроля. Автоматика и телемеханика, 2014, №8, стр. 131-145.

- [9]. Freiman C.V. Optimal Error Detection Codes for Completely Asymmetric Binary Channels. Information and Control, 1962, Vol. 5, Issue 1, pp. 64-71, doi: 10.1016/S0019-9958(62)90223-1.

- [10]. Burkatovskaya Yu.B., Butorina N.B., Matrosova A.Yu. Self-Testing Checker Design for Arbitrary Number of Code Words of (m,n) code. Proceedings of the 10th International Baltic Electronic Conference (BEC`2006), Tallinn, Estonia, October 2-4, 2006, pp. 183-186, doi: 10.1109/BEC.2006.311093.

- [11]. Слабаков Е.В., Согомонян Е.С. Самопроверяемые вычислительные устройства и системы (обзор). Автоматика и телемеханика, 1981, №11, стр. 147-167.

- [12]. Nicolaidis M., Zorian Y. On-Line Testing for VLSI A Compendium of Approaches. Journal of Electronic Testing: Theory and Applications, 1998, №12, pp. 7-20. DOI: 10.1023/A:1008244815697.

- [13]. Matrosova A.Yu., Levin I., Ostanin S.A. Self-Checking Synchronous FSM Network Design with Low Overhead. VLSI Design, 2000, Vol. 11, Issue 1, pp. 47-58. DOI: 10.1155/2000/46578.

- [14]. Tshagharyan G., Harutyunyan G., Shoukourian S., Zorian Y. Experimental Study on Hamming and Hsiao Codes in the Context of Embedded Applications. Proceedings of 15th IEEE East-West Design & Test Symposium (EWDTS`2017), Novi Sad, Serbia, September 29 – October 2, 2017, pp. 1-4.

- [15]. Аксёнова Г.П. Необходимые и достаточные условия построения полностью проверяемых схем свертки по модулю 2. Автоматика и телемеханика, 1979, №9, стр. 126-135.

- [16]. Гессель М., Согомонян Е.С. Построение самотестируемых и самопроверяемых комбинационных устройств со слабонезависимыми выходами. Автоматика и телемеханика, 1992, № 8 стр. 150-160.

- [17]. Busaba F.Y., Lala P.K. Self-Checking Combinational Circuit Design for Single and Unidirectional Multibit Errors // Journal of Electronic Testing: Theory and Applications, 1994, Issue 1, pp. 19-28. DOI: 10.1007/BF00971960.

- [18]. Morosow A, Saposhnikov V.V., Saposhnikov VI.V., Goessel M. Self-Checking Combinational Circuits with Unidirectionally Independent Outputs. VLSI Design, 1998, Vol. 5, Issue 4m pp. 333-345. DOI: 10.1155/1998/20389.

- [19]. Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D. New Methods of Concurrent Checking: Edition 1. – Dordrecht: Springer Science+Business Media B.V., 2008, 184 p.

- [20]. Ефанов Д.В., Сапожников В.В., Сапожников Вл.В. Условия обнаружения неисправности логического элемента в комбинационном устройстве при функциональном контроле на основе кода Бергера. Автоматика и телемеханика, 2017, №5, стр. 152-165.

- [21]. Сапожников В.В., Сапожников Вл.В., Ефанов Д.В., Дмитриев В.В. Новые структуры систем функционального контроля логических схем. Автоматика и телемеханика, 2017, №2, стр. 127-143.

- [22]. Мехов В.Б., Сапожников В.В., Сапожников Вл.В. Контроль комбинационных схем на основе модифицированных кодов с суммированием. Автоматика и телемеханика, 2008, №8, стр. 153-165.

- [23]. Ефанов Д.В., Сапожников В.В., Сапожников Вл.В. О свойствах кода с суммированием в схемах функционального контроля. Автоматика и телемеханика, 2010. №6, стр. 155-162.

- [24]. Блюдов А.А., Ефанов Д.В., Сапожников В.В., Сапожников Вл.В. Построение модифицированного кода Бергера с минимальным числом необнаруживаемых ошибок информационных разрядов. Электронное моделирование, 2012, Том 34, №6, стр. 17-29.

- [25]. Сапожников В.В., Сапожников Вл.В., Ефанов Д.В. Модульно-взвешенные коды с суммированием с наименьшим общим числом необнаруживаемых ошибок в информационных векторах. Электронное моделирование, 2017, Том 39, №4

- [26]. Сапожников В.В., Сапожников Вл.В., Ефанов Д.В., Котенко А.Г. Модульные коды с суммированием взвешенных переходов с последовательностью весовых коэффициентов, образующей натуральный ряд чисел. Труды СПИИРАН, 2017, №1, стр. 137-164, doi: 10.15622/SP.50.6.

- [27]. Lala P.K. Self-Checking and Fault-Tolerant Digital Design. San Francisco: Morgan Kaufmann Publishers, 2001, 216 p.

- [28]. Hamming R.W. Error Detecting and Correcting Codes. Bell System Technical Journal, 1950, 29 (2), pp. 147-160

- [29]. Sapozhnikov V., Sapozhnikov VI., Efanov D., Dmitriev V. Weighted Sum Code Without Carries – is an Optimum Code with Detection of Any Double Errors in Data Vectors // Proceedings of 14<sup>th</sup> IEEE East-West Design & Test Symposium (EWDTS`2016), Yerevan, Armenia, October 14-17, 2016, pp. 134-141, doi: 10.1109/EWDTS.2016.7807686.

- [30]. Sapozhnikov V., Sapozhnikov VI., Efanov D., Dmitriev V. New Sum Code for Effective Detection of Double Errors in Data Vectors // Proceedings of 13<sup>th</sup> IEEE East-West Design & Test Symposium (EWDTS`2015), Batumi, Georgia, September 26-29, 2015, pp. 154-159, doi: 10.1109/EWDTS.2015.7493123.

- [31]. Сапожников В.В., Сапожников Вл.В., Ефанов Д.В., Дмитриев В.В. Код с суммированием взвешенных информационных разрядов без переносов в системах функционального контроля. Автоматика на транспорте, 2017, Том 3, №3, стр. 414-433.

- [32]. Ghosh S., Basu S., Touba N.A. Synthesis of Low Power CED Circuits Based on Parity Codes. Proceedings of 23rd IEEE VLSI Test Symposium (VTS'05), 2005, pp. 315-320.

- [33]. Аксёнова Г.П. О функциональном диагностировании дискретных устройств в условиях работы с неточными данными. Проблемы управления, 2008, №5, стр. 62-66.

# Modified codes with weighted-transitions summation in concurrent error detection systems of combinational circuits

<sup>1</sup> D.V. Efanov <TrES-4b@yandex.ru> V.V. Sapozhnikov <port.at.pgups@gmail.com> Vl.V. Sapozhnikov <at.pgups@gmail.com> <sup>1</sup> Emperor Alexandex I St. Petersburg state transport university, 190031, Russia, St. Petersburg, Moscowsky ave., 9

**Abstract**. A method for constructing modified codes with summation of weighted transitions between bits in data vectors occupying neighboring positions is proposed. New codes with summation have the same number of check bits as the classic Berger codes, but they detect more errors in data vectors. Modified codes with summation of weighted transitions in comparison with Berger codes also have improved error detection characteristics in the area of small multiplicity. In addition, for some values of the lengths of information vectors codes can be constructed with the detection of any twofold and any triple errors. The authors developed a method for synthesizing concurrent error detection systems of combinational circuits, based on the analysis of the topology of the object of diagnosis with the selection of groups of checkable outputs, taking into account the properties of error detection by modified codes with summation of weighted transitions. An algorithm for the synthesis of a concurrent error detection systems has been developed.

**Keywords:** concurrent error-detection system; combinational circuit; Berger code; weight-transition sum code; double errors detection; triple errors detection.

**DOI:** 10.15514/ISPRAS-2017-29(5)-3

**For citation:** Sapozhnikov V.V., Sapozhnikov VI.V., Efanov D.V. Modified codes with weighted-transitions summation in concurrent error detection systems of combinational circuits. *Trudy ISP RAN/Proc. ISP RAS*, vol. 29, issue 5, 2017. pp. 39-60 (in Russian). DOI: 10.15514/ISPRAS-2017-29(5)-3

#### References

- [1]. McCluskey E.J. Logic Design Principles: With Emphasis on Testable Semicustom Circuits. N.J., Prentice Hall PTR, 1986, 549 p.

- [2]. Sogomonjan E.S., Slabakov E.V. [Self-checking devices and fault-tolerant systems]. Moscow: Radio i svjaz', 1989, 207 p. (in Russian).

- [3]. Goessel M., Graf S. Error Detection Circuits. London: McGraw-Hill, 1994, 261 p.

- [4]. Mitra S., McCluskey E.J. Which Concurrent Error Detection Scheme to Choose? Proceedings of International Test Conference, 2000, USA, Atlantic City, NJ, 03-05 October 2000, pp. 985-994, doi: 10.1109/TEST.2000.894311.

- [5]. Berger J.M. A Note on Error Detection Codes for Asymmetric Channels. Information and Control, 1961, Vol. 4, Issue 1, pp. 68-73, doi: 10.1016/S0019-9958(61)80037-5.

- [6]. Piestrak S.J. Design of Self-Testing Checkers for Unidirectional Error Detecting Codes. Wrocław: Oficyna Wydawnicza Politechniki Wrocłavskiej, 1995, 111 p.

- [7]. Das D., Touba N.A. Synthesis of Circuits with Low-Cost Concurrent Error Detection Based on Bose-Lin Codes. Journal of Electronic Testing: Theory and Applications, 1999, Vol. 15, Issue 1-2, pp. 145-155, doi: 10.1023/A:1008344603814.

- [8]. Bljudov A.A., Efanov D.V., Sapozhnikov V.V., Sapozhnikov Vl.V. On Codes with Summation of Unit Bits In Concurrent Error Detection Systems. Automation and remote control, 2014, Vol. 75, Issue 8, pp. 1460-1470, doi: 10.1134/S0005117914080098.

- [9]. Freiman C.V. Optimal Error Detection Codes for Completely Asymmetric Binary Channels. Information and Control. 1962, Vol. 5, Iissue 1, pp. 64-71, doi: 10.1016/S0019-9958(62)90223-1.

- [10]. Burkatovskaya Yu.B., Butorina N.B., Matrosova A.Yu. Self-Testing Checker Design for Arbitrary Number of Code Words of (m,n) code. Proceedings of the 10th International Baltic Electronic Conference (BEC`2006), Tallinn, Estonia, October 2-4, 2006, pp. 183-186, doi: 10.1109/BEC.2006.311093.

- [11]. Slabakov E.V., Sogomonjan E.S. Self-check computing devices and systems (survey). Automation and remote control, 1981, Vol. 42, Issue 11, pp. 1551-1566.

- [12]. Nicolaidis M., Zorian Y. On-Line Testing for VLSI A Compendium of Approaches. Journal of Electronic Testing: Theory and Applications, 1998, №12, pp. 7-20, doi: 10.1023/A:1008244815697.

- [13]. Matrosova A.Yu., Levin I., Ostanin S.A. Self-Checking Synchronous FSM Network Design with Low Overhead. VLSI Design, 2000, Vol. 11, Issue 1, pp. 47-58, doi: 10.1155/2000/46578.

- [14]. Tshagharyan G., Harutyunyan G., Shoukourian S., Zorian Y. Experimental Study on Hamming and Hsiao Codes in the Context of Embedded Applications. Proceedings of 15th IEEE East-West Design & Test Symposium (EWDTS`2017), Novi Sad, Serbia, September 29 – October 2, 2017, pp. 1-4.

- [15]. Aksjonova G.P. Necessary and sufficient conditions for design of completely checkable modulo 2 convolution circuits. Automation and remote control, 1979, Vol. 40, Issue 9, pp. 1362-1369.

- [16]. Gessel' M., Sogomonjan E.S. Design of self-testing and self-checking combinational circuits with weakly independent outputs. Automation and remote control, 1992, Vol. 53, Issue 8, pp. 1264-1272.

- [17]. Busaba F.Y., Lala P.K. Self-Checking Combinational Circuit Design for Single and Unidirectional Multibit Errors. Journal of Electronic Testing: Theory and Applications, 1994, Issue 1, pp. 19-28, doi: 10.1007/BF00971960.

- [18]. Morosow A, Saposhnikov V.V., Saposhnikov VI.V., Goessel M. Self-Checking Combinational Circuits with Unidirectionally Independent Outputs. VLSI Design, 1998, Vol. 5, Issue 4, pp. 333-345, doi: 10.1155/1998/20389.

- [19]. Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D. New Methods of Concurrent Checking: Edition 1. Dordrecht: Springer Science+Business Media B.V., 2008, 184 p.

- [20]. Efanov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. Conditions for Detecting a Logical Element Fault in a Combination Device under Concurrent Checking Based on Berger's Code. Automation and remote control, 2017, Vol. 78, Issue 5, pp. 892-902, doi: 10.1134/S0005117917040113.

- [21]. Sapozhnikov V.V., Sapozhnikov VI.V., Efanov D.V., Dmitriev V.V. New Structures of the Concurrent Error Detection Systems for Logic Circuits, Automation and remote control, 2017, Vol. 78, Issue 2, pp. 300-313, doi: 10.1134/S0005117917020096.

- [22]. Mehov V.B., Sapozhnikov V.V., Sapozhnikov Vl.V. Checking of combinational circuits basing on modification sum codes. Automation and remote control, 2008, Vol. 69, Issue 8, pp. 1411-1422.

- [23]. Efanov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. On Summation Code Properties In Functional Control Circuits. Automation and remote control, 2010, Vol. 71, Issue 6, pp. 1117-1123, doi: 10.1134/S0005117910060123.

- [24]. Bljudov A.A., Efanov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. Formation of the Berger Modified Code with Minimum Number of Undetectable Errors of Informational Bits. Jelektronnoe modelirovanie [Electronic Modeling], 2012, Vol. 34, Issue 6, pp. 17-29. (in Russian).

- [25]. Sapozhnikov V.V., Sapozhnikov Vl.V., Efanov D.V. Modulo weighted codes with summation with minimum number of undetectable errors in data vectors. Jelektronnoe modelirovanie [Electronic Modeling], 2017, Vol. 39, Issue 4 (in Russian).

- [26]. Sapozhnikov V.V., Sapozhnikov Vl.V., Efanov D.V., Kotenko A.G. Modulo Codes with Summation of Weighted Transitions With Natural Number Sequence of Weights. SPIIRAS Proceedings, 2017, Issue 1, pp. 137-164, doi: 10.15622/SP.50.6.

- [27]. Lala P.K. Self-Checking and Fault-Tolerant Digital Design. San Francisco: Morgan Kaufmann Publishers, 2001, 216 p.

- [28]. Hamming R.W. Error Detecting and Correcting Codes. Bell System Technical Journal, 1950, 29 (2), pp. 147-160, MR0035935.

- [29]. Sapozhnikov V., Sapozhnikov VI., Efanov D., Dmitriev V. Weighted Sum Code Without Carries – is an Optimum Code with Detection of Any Double Errors in Data Vectors. Proceedings of 14<sup>th</sup> IEEE East-West Design & Test Symposium

- (EWDTS`2016), Yerevan, Armenia, October 14-17, 2016, pp. 134-141, doi: 10.1109/EWDTS.2016.7807686.

- [30]. Sapozhnikov V., Sapozhnikov VI., Efanov D., Dmitriev V. New Sum Code for Effective Detection of Double Errors in Data Vectors. Proceedings of 13<sup>th</sup> IEEE East-West Design & Test Symposium (EWDTS`2015), Batumi, Georgia, September 26-29, 2015, pp. 154-159, doi: 10.1109/EWDTS.2015.7493123.

- [31]. Sapozhnikov V.V., Sapozhnikov VI.V., Efanov D.V., Dmitriev V.V. Code with summation of weighted data bits without transitions within concurrent error detection systems. Avtomatika na transporte [Automation on transport], 2017, Vol. 3, Issue 3, pp. 414-433 (in Russian).

- [32]. Ghosh S., Basu S., Touba N.A. Synthesis of Low Power CED Circuits Based on Parity Codes, Proceedings of 23rd IEEE VLSI Test Symposium (VTS'05), 2005, pp. 315-320.

- [33]. Aksjonova G.P. On functional diagnosis of discrete devices under imperfect data processing conditions. Problemy upravlenija [Control Sciences], 2008, Issue 5, pp. 62-66 (in Russian).